# DESIGN OF LOW POWER-HIGH SPEED BINARY ADDER USING REVERSIBLE LOGIC

Jugal Kishore Bhandari<sup>1</sup>, S.KrishnaPriya<sup>2</sup>, Md Touseef Sumer<sup>3</sup> <sup>1,3</sup>Asst Professor, <sup>2</sup>Associate Professor - Department of E.C.E, Geethanjali college of Engineering and Technology, Hyderabad, India.

ABSTRACT: Reversibility plays a fundamental role when computations with minimal energy dissipation are considered. In recent years, reversible logic has emerged as one of the most important approaches for power optimization. A reversible logic design will not result in loss of information; this avoids the unwanted heat generated. For power not to be dissipated in an arbitrary circuit, it must be built from reversible gates. In computers and other kinds of processors, adders are used not only in the ALU(s), but also in other parts of the processor, where they are used to calculate addresses, table indices, and in digital electronics, adder performs addition of two numbers. This research proposes a new implementation of adder in reversible logic. The power requirements of traditional methods used to increase performance are too great. It has been proven that use of traditional irreversible logic gates, leads to power dissipation regardless of underlying technology. The proposed design reduces the number of gate operations compared to the existing adder reversible logic implementations. So, this design gives rise to an implementation with a reduced area and delay. We can use it to construct more complex systems in nanotechnology. The high speed adder circuit using Hardware Description Language (HDL) is constructed and verified in the platform Xilinx ISE 9.2i and synthesized using nc-sim and virtuoso of cadence in 180nm Technology to analyze the design parameters.

Keywords: High Speed Adder, Reversible logic, Garbage output, irreversible gates.

# I. INTRODUCTION

The core of every microprocessor, digital signal processor (DSP), and data- processing application-specific integrated circuit (ASIC) is its data path. It is often the crucial circuit component if die area, power dissipation, and especially operation speed are of concern. At the heart of data-path and addressing units in turn are arithmetic units, such as comparators, adders, and multipliers. Finally, the basic operation found in most arithmetic components is the binary addition. Besides of the simple addition of two numbers, adders are also used in more complex operations like multiplication and division. But also simpler operations like incrementation and magnitude comparison base on binary addition. Therefore, binary addition is the most important arithmetic operation. [2] It is also a very critical one if implemented in hardware because it involves an expensive carry-propagation step, the evaluation time of which is dependent on the operand word length. The efficient implementation of the addition operation in an integrated

circuit is a key problem in VLSI design.

# 1.1 Adder circuits

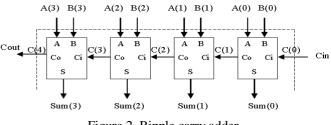

Several types of adders are used in computing systems. A ripple carry adder has the simplest structure. In a ripple carry adder, full adders connected in series generate the sum and the carry outputs based on the addend bits and the carry input. The disadvantage of a ripple carry adder is that the carry has to propagate through all stages.

1.2 Full Adder

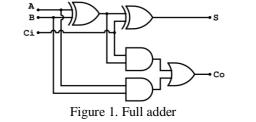

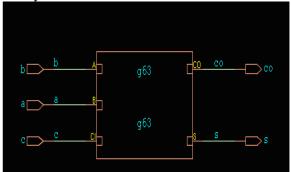

A Full Adder (FA) is a logical circuit that performs an addition operation on three binary digits. The full adder produces a sum and a carry value, which are both binary digits. The logical diagram of full adder is shown in figure 1.

A FA adds binary numbers and accounts for values carried in as well as out. A one-bit full adder adds three one-bit numbers, often written as A, B, and  $C_i$  here A, B are the operands, and  $C_i$  is a bit carried in (in theory from a past addition by [3]). The circuit produces a two-bit output sum typically represented by the signals  $C_0$  (Carry) and S (Sum). The Boolean equation and truth table are shown bellow.

(1) S = a xor b xor c; (2) Co = ab + bc

+ ca ;

1.3 Ripple carry adders

The basic building block of a ripple carry adder is a full adder block. A full adder computes the sum bit Si and the carry output c i+1 based on addend inputs a and b and carry input c. The output expressions for a ripple carry adder are

(1) Si = a xor b xor c; bc + ca ; (i = 0,1,2,...) (2) Ci+1 = ab +

It is possible to create a logical circuit using multiple full adders to add *N*-bit numbers. Each full adder inputs a carry

$C_{in}$  that is the  $C_{out}$  of the previous adder. This kind of adder is a Ripple Carry Adder (RCA) in [3], since each carry bit "ripples" to the next full adder. However, the ripple carry adder is relatively slow, since each full adder must wait for the carry bit is which coming from the previous full adder. The RCA is shown in figure. 2.

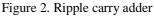

#### 1.4 Carry - Select Adder

Carry Select Adders (CSLA) use multiple narrow adders to create fast wide adders. Consider the addition of two n bit numbers with  $a = a_{n-1}...a_0$ , and  $b = b_{n-1}...b_0$ . At the bit

level the adder delay increases from the least significant 0<sup>th</sup>

position upward, with the  $(n-1)^{th}$  requiring the most complex logic. A carry select adder breaks the addition problem into smaller groups. A carry-select adder provides two separate adders for the upper words, one for each possibility. A multiplexer (MUX) is then used to select the valid result. The figure 3 shows the block diagram of CSLA. As a concrete example, consider an 8-bit adder that is split into two 4-bit groups. The lower order bits  $a_3 a_2 a_1 a_0$  and  $b_3 b_2 b_1 b_0$  are fed into the 4-bit adder to produce the sum bits  $S_3 S_2 S_1 S_0$  and a carry-out bit  $C_4$  as shown.

# II. INTRODUCTION TO REVERSIBLE LOGIC

A Reversible circuit/gate can generate unique output vector from each input vector, and vice versa, i.e., there is a one to one correspondence between the input and output vectors. Thus, the number of outputs in a reversible gate or circuit has the same as the number of inputs, and commonly used traditional NOT gate is the only reversible gate. Each Reversible gate has a cost associated with it called Quantum cost. The Quantum cost of a Reversible gate is the number of 2\*2 Reversible gates or Quantum logic gates required in designing. One of the most important features of a Reversible gate is its garbage output i.e., every input of the gate, which is not used as input to other gate or as a primary output is called garbage output. Minimization of the number of Reversible gates, Quantum cost and garbage inputs/outputs are the focus of research in Reversible logic [3].

Reversible logic is a promising computing design paradigm, which presents a method for constructing computers that produce no heat dissipation. Reversible computing emerged as a result of the application of quantum mechanics principles towards the development of a universal computing machine. Specifically, the fundamentals of reversible computing are based on the relationship between entropy, heat transfer between molecules in a system, the probability of a quantum particle occupying a particular state at any given time, and the quantum electrodynamics between electrons when they are in dose proximity. A reversible logic gate is an N-input N-output logic device that provides one to one mapping between the input and the output. It not only helps us to determine the outputs from the inputs but also helps us to uniquely recover the inputs from the outputs.

- Garbage outputs are those, which do not contribute to the reversible logic realization of the design.

- Quantum cost refers to the cost of the circuit in terms of the cost of a primitive gate.

- Gate count is the number of reversible gates used to realize the function.

- Gate level refers to the number of levels which are required to realize the given logic functions.

The following are the important design constraints for reversible logic circuits. [1]

1. Reversible logic gates do not allow fan-outs.

2. Reversible logic circuits should have minimum quantum cost.

3. The design can be optimized so as to produce minimum number of garbage outputs.

4. The reversible logic circuits must use minimum number of constant inputs.

5. The reversible logic circuits must use a minimum logic depth or gate levels.

# III. III PROPOSED DESIGN

Basic operation, structure, Quantum cost has been explained in many papers. So the available designs of full adder using basic reversible logic gates take more area, power and have more delay.

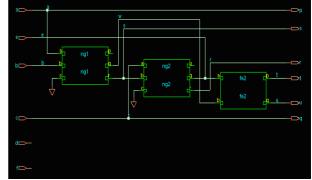

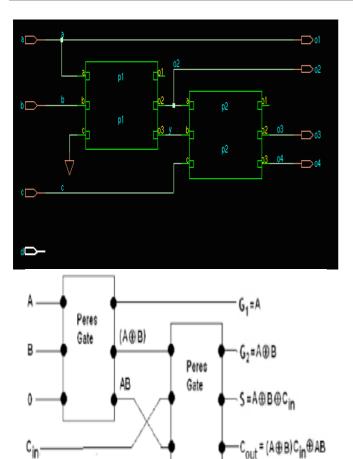

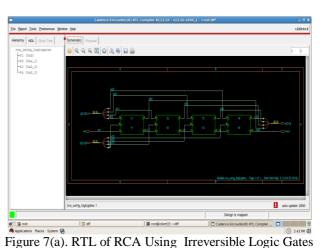

Figure 4. RTL of Full Adder Using Irreversible Logic Gates

Figure 5. RTL of Full Adder Using Proposed NGFE Logic

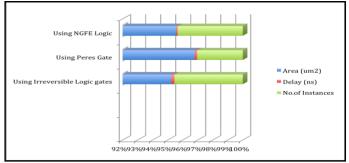

Figure 6. RTL of Full Adder Using Peres Gates A new design for full adder is proposed in this paper, which uses the conventional new gate, and Feynman gate but results with less area, power and delay. Also when compared with irreversible logic gates it provides all the parameters with less values. The proposed full-adder is designed in Verilog HDL and synthesized using cadence nc-sim simulator. The parameter results, shows a drastic improvement when compared to irreversible logic gates and conventional design using peresgate. The full adder features are specified in Table I for designs using irreversible logic, conventional peresgate and proposed NGFE logic based full adder. Figure 4 shows the schematic of full adder using basic logic gates with specified three inputs a, b, cin and two outputs cout, sum. This full adder design is universal consisting of EXOR gates, AND gates and OR-gate and the design factors are specified in table. The Figure 6 shows the schematic of full adder designed using two three input peres gates making it a 4 input 4 output full adder with inputs a, b, cin and one constant input with logic-0 and outputs sum and carry with two more garbage outputs. The design has comparatively improved design factors than a basic irreversible logic based full adder. Figure 5 shows Proposed new gate and Feynman gate based adder making it a 6 input 6 output circuit. The RCA is used to design the 4bit CSA, which is constructed using logic gates, peres gate and proposed adder too. The constraint parameters of VLSI design are listed in table-II for RCA. Figure 7,8 and 9 shows the schematic structure of RCA and RCA based CSA respectively.

Figure 7(b). RTL of CSA Using Irreversible Logic Gates TABLE-I TABLE-II

| Full<br>Adder                            | Are<br>a<br>(um<br>2) | Power (nW)               |                          |                    | Dela<br>y | No.<br>of         | Ripple<br>Carry                          | Are       | Power (uW)               |                          |                    | Dela<br>y | No.<br>of         |

|------------------------------------------|-----------------------|--------------------------|--------------------------|--------------------|-----------|-------------------|------------------------------------------|-----------|--------------------------|--------------------------|--------------------|-----------|-------------------|

|                                          |                       | Leak<br>age<br>Pow<br>er | Dyn<br>amic<br>Pow<br>er | Total<br>Pow<br>er | (nS)      | Inst<br>anc<br>es | Adder                                    | (um<br>2) | Leak<br>age<br>Pow<br>er | Dyn<br>amic<br>Pow<br>er | Total<br>Pow<br>er | (nS)      | Inst<br>anc<br>es |

| Using<br>Irreversibl<br>e Logic<br>gates | 70                    | 3.63<br>2                | 4.43<br>9                | 4.44<br>3          | 0.49      | 1                 | Using<br>Irreversibl<br>e Logic<br>gates | 279       | 0.01<br>53               | 21.6<br>44               | 21.6<br>59         | 1.48<br>4 | 4                 |

| Ūsing<br>Peres<br>Gate                   | 96                    | 4.11<br>6                | 3.54<br>6                | 3.55               | 0.68<br>6 | 3                 | Using<br>Peres<br>Gate                   | 386       | 0.01<br>64               | 16.1<br>25               | 16.1<br>42         | 1.37<br>8 | 12                |

| Using<br>NGFE<br>Logic                   | 53                    | 2.42<br>2                | 0.97<br>1                | 0.97<br>3          | 0.47<br>7 | 3                 | Using<br>NGFE<br>Logic                   | 213       | 0.00<br>968              | 3.93<br>9                | 3.94<br>9          | 0.47<br>6 | 12                |

Figure 8(a). RTL of RCA Using Peres Gate

Figure 8(b). RTL of CSA Using Peres gate

Figure 9(a). RTL of RCA Using Proposed NGFE Logic

Figure 9(b). RTL of CSA Using Proposed NGFE Logic

# IV. ANALYSIS AND TOOL SIMULATION

To evaluate performance; the adder structures discussed in this paper are designed using 180nm CMOS technology using cadence-virtuoso and ncsim. The virtuoso tool integrates traditionally separated front-end and back-end chip design into an integrated flow, accelerating the design cycle and reduced design complexities.

#### TABLE-III

| Carry Select<br>Adder (CSA)<br>based on | Area<br>(um |               | Power (uW)       | Delay<br>(nS) | No.of<br>Instances |    |

|-----------------------------------------|-------------|---------------|------------------|---------------|--------------------|----|

|                                         | 2)          | Leakage Power | Dynamic<br>Power | Total Power   |                    | 2  |

| Using<br>Irreversible<br>Logic gates    | 669         | 0.2830        | 33.532           | 33.560        | 1.523              | 32 |

| Using Peres<br>Gate                     | 858         | 0.03765       | 29.222           | 29.260        | 1.454              | 27 |

| Using NGFE<br>Logic                     | 639         | 0.03509       | 9.1216           | 9.1567        | 0.744              | 29 |

It tightly integrates mixed-signal implementation with digital implementation, circuit simulation, transistor level extraction and verification. All simulations are carried out at nominal conditions: VDD=1.8V, I/O supply voltage: 1V. Table I shows the drastically reduction in all the major parameters for making a useful design. Table III shows the comparison of area power and timing of irreversible logic gates, peres gate and reversible logic gate. This Proposed design has very less consumption of area and power with less delay from input to carry output.

Figure 10. Graphical representation of % of area covered, Power consumed and speed in comparison with logic gates and peres gate.

# V. CONCLUSION

The implementations of three types of adders, ripple carry adder, and carry select adder, using reversible logic gate is shown. Results show that the proposed design in more efficient adder in terms of area and power consumption with account of more garbage outputs than those using the logic gates and better in all terms when compared to adder using peres gate.

# REFERENCES

- [1] Design of high speed, low power Reversible Logic Adder using HNG gate- M Singh Sankhwar et al Int. Journal of Engineering Research and Applications. ISSN: 2248-9622, Vol. 4, Issue 1(Version 2), January 2014, pp.152-159

- [2] Reversible Adder Derek Schmidlkofer Homework 1ECE 590 4-26-06.

- [3] Design Of Adder / Subtractor Circuits Based On Reversible Gates V.Kamalakannan, Shilpakala.V, Ravi.H.N ISSN (Online): 2278 – 8875 ; International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering Vol. 2, Issue 8, August 2013.

- [4] High-Speed VLSI Arithmetic Units: Adders and

Multipliers by Prof. Vojin G. Oklobdzija.

- [5] Area, Delay and Power Comparison of Adder Topologies R.UMA,Vidya Vijayan, M. Mohanapriya, Sharon Paul

- [6] International Journal of VLSI design & Communication Systems (VLSICS) Vol.4, No.4, August 2013 low power-area designs of 1bit full adder in cadence virtuoso platform-karthik reddy. g.

- [7] International Journal of Computer Applications (0975 – 8887) Volume 29– No.10, September 2011 VLSI Implementation of Adders for High Speed ALU Prashant Gurjar.

- [8] Wseas Transactions On Circuits And Systems P. K. Lala, J. P. Parkerson, P. Chakraborty Adder Designs using Reversible Logic Gates ISSN: 1109-2734 369 Issue 6, Volume 9, June 2010.

# About Authors:

Jugal Kishore Bhandari received the B.E. degree in Electronics & communication engineering from Anna University, Chennai, India, in 2007 and Masters of Engineering from Anurag Group of Institutions Formerly known CVSR College of engineering, Ghatkesar, hyd, presently he is working as assistant professor at Geethanjali college of engineering and technology, Hyd. His areas of interest are low power design, fault tolerant system designing and digital electronics.

S.Krishnapriya obtained her B. Tech degree in Electronics and Communication Engineering from J.N.T.U, Hyderabad in 2002 and M.E in Communication Engineering from osmania University in the year 2004.. She had 9 years of teaching experience. Presently she is Associate Professor at Geethanjali College of engineering and technology, Hyd. Her fields of interests are Analog and Digital communications, Microwave engineering.

Md Touseef Sumer currently working as assistant professor at Geethanjali College of engineering and technology, Hyd. He pursued his M.Tech (Systems and Signals) from JNTU College of engineering Hyderabad and completed his Bachelors in Electronics & communication engineering from J.N.T.U, Hyderabad. His areas of interest are Signal processing, wireless communication and digital electronics.