# DESIGN AND IMPLEMENTATION OF A NOVEL AREA-EFFICIENT 48X48ANT MULTIPLIER

P.Rama Koteswara Rao<sup>1</sup>, Ch. Naveena Priyadarsini<sup>2</sup>

<sup>1</sup>M.Tech Student, <sup>2</sup>Assistant Professor

Dept of ECE, Narasaraopeta Institute Of Technology, Kotappakonda Road, Yellamanda Post, Narasaraopet Mandal, Guntur District, Andhra Pradesh, India.

Abstract: In this paper, we tend to propose a solid lowcontrol number style by receiving recursive clamor tolerant (RCT) outline with the settled width number to influence the lessened exactness to copy excess piece. The arranged hymenopteran configuration will take care of the demand of high accuracy, low power utilization, and space strength. We tend to style the settled width RPR with mistake remuneration circuit by means of dissecting of possibility and measurements. Exploitation the incomplete item terms of information amendment vector and minor information redress vector to bring down the truncation mistakes, the equipment many-sided quality of blunder remuneration circuit might be streamlined, in an exceedingly 48×48 piece hymenopteran number, circuit space in our settled width RPR might be around forty four,55% and power utilization in our hymenopteran style might be spared by twenty third as contrasted and the condition of-craftsmanship hymenopteran style.

### I. INTRODUCTION

The ascent of transportable and wireless computing systems in recent years drives the requirement for ultralow power systems. To lower the facility dissipation, offer Voltage scaling is wide used as an efficient low-power technique since the facility consumption in CMOS circuits is proportional to the sq. of offer voltage. However, in deep-sub micrometer process technologies, noise interference issues have raised problem to style the reliable and economical electronics systems; thus, the planning techniques to reinforce noise tolerances are wide developed. An aggressive low-power technique, brought up as voltage over scaling (VOS), was projected in to lower offer voltage on the far side vital offer voltage while not sacrificing the output. However, VOS ends up in severe degradation in signal-to-noise (SNR). a completely unique recursive noise tolerant (ANT) technique combined VOS main block with reduced-precision reproduction (RPR), that combats soft errors effectively whereas achieving vital energy saving. Some hymenopteran deformation styles area unit given in and therefore the hymenopterans style conception is more extended to system level. However, the RPR styles within the hymenopterous insect styles are designed in a much customized manner, that isn't simply adopted and perennial. The RPR styles within the hymenopterous insect style will operate in a very in no time manner, however their hardware complexness is simply too advanced. As a result, the RPR style within the hymenopterous insect style of remains the foremost common style due to its simplicity. However, adopting with RPR in

ought to still pay further space overhead and power consumption. In this paper, we have a tendency to additional projected a straightforward means victimization the fixed-width RPR to switch the full-width RPR block. Victimization the fixed-width RPR, the computation error will be corrected with lower power consumption and lower space overhead. We have a tendency to take use of chance, statistics, and partial product weight analysis to seek out the approximate compensation vector for a lot of precise RPR style so as to not increase the crucial path delay, we have a tendency to prohibit the compensation circuit in RPR should not be set within the crucial path. As a result, we will notice the hymenopterous insect style with smaller circuit space, lower power consumption, and lower crucial provide voltage.

## II. EXISTING ANT ARCHITECTURE DESIGNS

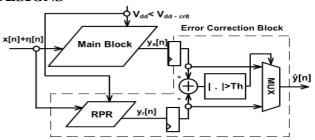

Fig.1. ANT architecture

The ANT technique includes both main digital signal processor (MDSP) and error correction (EC) block, as shown in Fig. 1. To meet ultralow power demand, VOS is used in MDSP. However, under the VOS, once the critical path delay Tcp of the system becomes greater than the sampling period Tsamp, the soft errors will occur. It leads to severe degradation in signal precision. In the ANT technique, a replica of the MDSP but with reduced precision operands and shorter computation delay is used as EC block. Under VOS, there are a number of input-dependent soft errors in its output ya[n]; however, RPR output yr[n] is still correct since the critical path delay of the replica is smaller than Tsamp. Therefore, vr[n] is applied to detect errors in the MDSP output ya[n]. Error detection isaccomplished by comparing the difference |ya[n] - yr[n]| against a threshold Th. Once the difference between ya[n] and yr[n] is larger than Th, the output y ildot [n] is yr[n] instead of ya[n]. As a result, y ildot [n] can be expressed as,

$$\hat{y}[n] = \begin{cases} y_a[n], & \text{if } |y_a[n] - y_r[n]| \le Th \\ y_r[n], & \text{if } |y_a[n] - y_r[n]| > Th. \end{cases}$$

Th is determined by

$$Th = \max_{\forall \text{input}} |y_o[n] - y_r[n]|$$

Where yo[n] is error free output signal. In this way, the power consumption can be greatly lowered while the SNR can still be maintained without severe degradation.

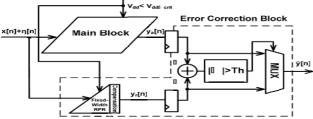

### II. PROPOSED ANT MULTIPLIER DESIGN USING FIXED WIDTH RPR

In this paper, we have a tendency to more planned the fixedwidth RPR to interchange the full-width RPR block within the hymenopter style, as shown in Fig. 2, which might not solely give higher computation exactness, lower power consumption, and lower space overhead in RPR, however conjointly perform with higher SNR, a lot of space economical, lower operative offer voltage, and lower power consumption in realizing the hymenopter design. We have a tendency to demonstrate our fixed-width RPR-based hymenopter style in Associate in nursing hymenopter number. The fixed-width styles are sometimes applied in DSP applications to avoid infinite growth of bit breadth isolating n-bit least important bit (LSB) output may be a widespread answer to construct a fixed-width DSP with n-bit input and n-bit output. The hardware complexness and power consumption of a fixed-width DSP is typically concerning 1/2 the full-length one. However, truncation of LSB half ends up in rounding, that must be paid exactly. Several literatures are conferred to cut back the misreckoning with constant correction price or with variable correction price. The circuit complexness to compensate with constant corrected price may be less complicated than that of variable correction value; but, the variable correction approaches at sometimes a lot of precise.

Fig.2. Proposed ANT architecture with fixed-width RPR. In their compensation technique is to compensate the miscalculation between the full-length multiplier factor and also the fixed-width multiplier factor. However, within the fixed-width RPR of associate Emmet multiplier factor, the compensation error we'd like to correct is that the overall miscalculation of MDSP block. Unlike, our compensation technique is to compensate the miscalculation between the full-length MDSP multiplier factor and also the fixed-width RPR multiplier factor. In today, there are several fixed-width

multiplier factor styles applied to the full-width multipliers. However, there's still no fixed-width RPR style applied to the Emmet multiplier factor styles. To attain a lot of precise error compensation, we have a tendency to compensate the miscalculation with variable correction worth. We have a tendency to construct the error compensation circuit in the main exploitation the partial product terms with the biggest weight within the least important section. The error compensation formula makes use of chance, statistics, and regression analysis to search out the approximate compensation worth. To avoid wasting hardware quality, the compensation vector within the partial product terms with the biggest weight within the least important section is directly inject into the fixed-width RPR, that doesn't want further compensation logic gates. To any lower the compensation error, we have a tendency to conjointly think about the impact of truncated merchandise with the second most vital bits on the error compensation. We have a tendency to propose a slip-up compensation circuit using a simple minor input correction vector to compensation the error remained. In order not to increase the critical path delay, we locate the compensation circuit in the noncritical path of the fixed-width RPR. As compared with the fullwidth RPR design in, the proposed fixed-width RPR multiplier not only performs with higher SNR but also with lower circuitry area and lower power consumption.

### A. Proposed Precise Error Compensation Vector for Fixed-Width RPR Design

In the hymenopter style, the perform of RPR is to correct the errors occurring within the output of MDSP and maintain the SNR of whole system whereas lowering provide voltage. Within the case of exploitation fixed-width RPR to comprehend hymenopter design, we tend to not solely lower circuit space and power consumption, however conjointly accelerate the computation speed as compared with the standard full-length RPR. However, we want to compensate immense misestimating attributable to pruning several hardware components within the LSB a part of MDSP.In the MDSP of n-bit ANT Baugh Wooley array multiplier, its two unsigned n-bit inputs of X and Y can be expressed as

$$X = \sum_{i=0}^{n-1} x_i \cdot 2^i, \qquad Y = \sum_{j=0}^{n-1} y_j \cdot 2^j.$$

The multiplication result P is the summation of partial products of xi y j, which is expressed as

$$P = \sum_{k=0}^{2n-1} p_k \cdot 2^k = \sum_{j=0}^{n-1} \sum_{i=0}^{n-1} x_i y_j \cdot 2^{i+j}.$$

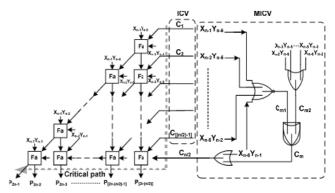

The (n/2)-bit unsigned full-width Baugh-Wooley partial product array can be divided into four subsets, which are most significant part (MSP), input correction vector  $[ICV(\beta)]$ , minorICV [MICV( $\alpha$ )], and LSP, as shown in Fig. 3. In the RPR, only MSP part is kept and the other parts are removed. Therefore, the other three parts of  $ICV(\beta)$ ,

MICV( $\alpha$ ), and LSP are called as truncated part. The truncated ICV( $\beta$ ) and MICV( $\alpha$ ) are the most important parts because of their highest weighting. Therefore, they can be applied to construct the truncation error compensation algorithm. To evaluate the accuracy of a fixed-width RPR, we can exploit the difference between the (n/2)-bit fixed-width RPR output and the 2n-bit full-length MDSP output, which is expressed as.

$$\varepsilon = P - P_t$$

Where P is the output of the complete multiplier in MDSP and Pt is the output of the fixed-widthmultiplier in RPR. Pt can be expressed as

$$P_{t} = \sum_{j=\frac{n}{2}+1}^{n-1} y_{j} 2^{j} \sum_{i=\frac{3n}{2}-j}^{n-1} x_{i} 2^{i}$$

$$+ f\left(x_{n-1}y_{\frac{n}{2}}, x_{n-2}y_{\frac{n}{2}+1}, x_{n-3}y_{\frac{n}{2}+2}, \dots, x_{\frac{n}{2}}y_{\frac{n}{2}+2}\right)$$

$$+ f\left(x_{n-2}y_{\frac{n}{2}}, x_{n-3}y_{\frac{n}{2}+1}, x_{n-4}y_{\frac{n}{2}+2}, \dots, x_{\frac{n}{2}}y_{n-2}\right)$$

$$= \sum_{j=\frac{n}{2}+1}^{n-1} y_{j} 2^{j} \sum_{i=\frac{3n}{2}-j}^{n-1} x_{i} 2^{i} + f(ICV) + f(MICV)$$

$$= \sum_{j=\frac{n}{2}+1}^{n-1} y_{j} 2^{j} \sum_{i=\frac{3n}{2}-j}^{n-1} x_{i} 2^{i} + f(EC)$$

Where f(EC) is the error compensation function, f(ICV) is the error compensation function contributed by the input correction vector  $ICV(\beta)$ , and f(MICV) is the error compensation function contributed by minor input correction vector  $MICV(\alpha)$ . The source of errors generated in the fixedwidth RPR is dominated by the bit products of ICV since they have the largest weight. It is reported that a low-cost EC circuit can be designed easily if a simple relationship between f(EC) and  $\beta$  is found. It is noted that  $\beta$  is the summation of all partial products of ICV. By statistically analyzing the truncated difference between MDSP and fixedwidth RPR with uniform input distribution.

### B. Proposed Precise Error Compensation Vector for Fixed-Width RPR Design

To realize the fixed-width RPR, we construct one directly injecting ICV( $\beta$ ) to basically meet the statistic distributionand one minor compensation vector MICV( $\alpha$ ) to amend the insufficient error compensation cases. The compensation vector ICV( $\beta$ ) is realized by directly injecting the partial terms of Xn-1 Yn/2, Xn-2Y(n/2)+1, Xn-3Y(n/2)+2,..., X(n/2)+2Yn-2. These directly injecting compensation terms are labeled asC1, C2, C3,..., C(n/2)-1 in Fig. 3.The other compensation vector used to mend the insufficient error compensation case is constructed by one conditional controlled OR gate. One input of OR gate is injected by X(n/2)Yn-1 , which is designed to realize the function of compensation vector  $\beta$ . The other input is conditional controlled by the judgment formula used to judge whether  $\beta=0$  and  $\beta l=0$  as well.

Fig. 3. Proposed high-accuracy fixed-width RPR multiplier with compensation constructed by the multiple truncation EC vectors combined ICV together with MICV.

The term Cm1 is used to judge whether  $\beta = 0$  or not. The judgment function is realized by one NOR gate, while its inputs are Xn-1 Yn/2, Xn-2Y(n/2)+1, Xn-3Y(n/2)+2,... X(n/2)+2Yn-2. The term Cm2 is used to judge whether  $\beta l =$ 0. The judgment function is realized by one OR gate, while its inputs are Xn-2Yn/2, Xn-3Y(n/2)+1, Xn-4Y(n/2)+2,... X(n/2)+1 Yn-2. If both of these two judgments are true, a compensation termCm is generated via a two-input AND gate. Then, Cm is injected together with X(n/2)Yn-1 into a two-input OR gate to correct the insufficient error compensation. Accordingly, in the case of  $\beta = 0$  and  $\beta l = 0$  as well, one additional carry-in signal C(n/2) is injected into the compensation vector to modify the compensation value as  $\beta$ + 1 instead of  $\beta$ . Moreover, the carry-in signal C(n/2) is injected in the bottom of error compensation vector, which is the farthest location away from the critical path. Therefore, not only theerror compensation precision in the fixed-width RPR can be enhanced, the computation delay will also not be postponed. Since the critical supply voltage is dominated by the critical delay time of the RPR circuit, preserving the critical path of RPR not be postponed is very important. Finally, the proposed high-precision fixed-width RPR multiplier circuit is shown in Fig. 3. In our presented fixedwidth RPR design, the adder cells can be saved by half as compared with the conventional full-width RPR. Moreover, the proposed high-precision fixed-width RPR design can even provide higher precision as compared with the fullwidth RPR design.

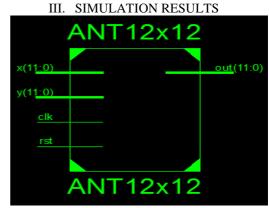

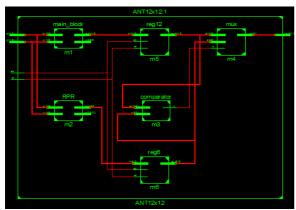

Fig.4. RTL of ANT Block

Fig.5.Schematic of the proposedarchitecture

| Name          | Value       | <br>1,999,800 ps | 1,999,850 ps       | 1,999,900 ps | 1,999,950 ps |

|---------------|-------------|------------------|--------------------|--------------|--------------|

| 🏣 cik         | 1           |                  |                    |              |              |

| 🍱 rst         | 0           |                  |                    |              |              |

| ▶ 🛂 x[11:0]   | 10101010101 |                  | 10101010101        | 0            |              |

| y[11:0]       | 10111101101 |                  | 10111101101        | 0            |              |

| ▶ 🛂 out[11:0] | 01111110011 |                  | 01111110011        | 0            |              |

| p[23:0]       | 01111110011 |                  | 011111110011000101 | 1000100      |              |

| q[11:0]       | 01111011011 |                  | 01111011011        | 0            |              |

| ▶ 👹 w1[11:0]  | 01111110011 |                  | 01111110011        | 0            |              |

| ya[11:0]      | 01111110011 |                  | 01111110011        | 0            |              |

| ▶ 👹 w2[5:0]   | 011110      |                  | 011110             |              |              |

| yr[5:0]       | 011110      |                  | 011110             |              |              |

| ∏g s          | 0           |                  |                    |              |              |

|               |             |                  |                    |              |              |

Fig.6.Simulation results

#### Extension

In this we propose a low error and area efficient fixed width RPR based 24\*24 bit ANT multiplier. The low-voltage low-power merit in the presented ANT design can still be preserved under process deviation and high-temperature environments. In this we use four 12\*12 ANT multipliers .As we are using 12\*12 bit width we can efficiently use our project in real time applications.

#### IV. CONCLUSION

In this paper, a low-error and area-efficient fixed-width RPR-based ANT multiplier design is presented. The proposed 48-bit ANT multiplier circuit is implemented in TSMC 90-nm process and its silicon area is 4616.5  $\mu$ m2. Under 0.6 V supply voltage and 200-MHz operating frequency, the power consumption is 0.393 mW. In the presented 12-bit by 12-bit ANT multiplier, the circuitry area in our fixed-width RPR can be saved by 45%, the lowest reliable operating supply voltage in our ANT design can be lowered to 0.623  $\nu$ DD, and power consumption in our ANT design can be saved by 23% as compared with the state-of-art ANT design.

#### REFERENCES

- [1] (2009). The International Technology Roadmap for Semiconductors[Online]. Available: http://public.itrs.net/

- [2] B. Shim, S. Sridhara, and N. R. Shanbhag, "Reliable low-power digital signal processing via reduced

- precision redundancy," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 12, no. 5, pp. 497–510, May 2004.

- [3] B. Shim and N. R. Shanbhag, "Energy-efficient soft-error tolerant digital signal processing," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 14, no. 4, pp. 336–348, Apr. 2006.

- [4] R. Hedge and N. R. Shanbhag, "Energy-efficient signal processing via algorithmic noise-tolerance," in Proc. IEEE Int. Symp. Low PowerElectron. Des., Aug. 1999, pp.

- [5] V. Gupta, D. Mohapatra, A. Raghunathan, and K. Roy, "Low-power digital signal processing using approximate adders," IEEE Trans. Comput.Added Des. Integr. Circuits Syst., vol. 32, no. 1, pp. 124–137, Jan. 2013.

- [6] Y. Liu, T. Zhang, and K. K. Parhi, "Computation error analysis in digital signal processing systems with overscaled supply voltage," IEEETrans. Very Large Scale Integr. (VLSI) Syst., vol. 18, no. 4, pp. 517–526, Apr. 2010.

- [7] J. N. Chen, J. H. Hu, and S. Y. Li, "Low power digital signal processing scheme via stochastic logic protection," in Proc. IEEE Int. Symp. CircuitsSyst., May 2012, pp. 3077–3080.