# **DESIGN SINGLE CYCLE MICROPROCESSOR USING VHDL**

Naveen Kumar Saini

Asst. Prof. EE, RTU, Shekhawati Institute Of Engineering, Sikar, India

Abstract: In this paper, a A microprocessor is a digital electronic component with transistors on a single semiconductor integrated circuit (IC).One or more microprocessors typically serve as a central processing unit(CPU) in a computer system or handheld device .Microprocessors made possible the advent of the microcomputer .Before this electronic CPUs were typically made from bulky discrete switching device containing the equivalent of only a few transistors .By integrating the processor onto one or a very few large-scale integrated circuit package, the cost of processor power was greatly reduced. Since the advent of the IC in the mid-1970s, the microprocessor has become the most prevalent implementation of the CPU, nearly completely replacing all others forms. This project is trying to design an 8 bit microprocessor by using VHDL .VHDL is stand for very high speed integrated circuit hardware description language .It is one of the most popular design application uses by most designers nowadays .The microprocessor will be synthesize in VHDL using Xilinx ISE. The 8 bit microprocessor is widely use in microcontroller devise with specific task because it has a specific task because it has a specific instruction where it only done a given instruction. Keorywords: integrated circuit (IC), VHDL, Xilinx

## I. INTRODUCTION

In this paper, Microprocessors are the heart of all "smart" devices, whether they be electronic devices or otherwise. Their smartness comes as a direct result of the decisions and controls that microprocessors make. For example, we usually do not consider a car to be an electronic device. However, it certainly has many complex, smart electronic systems, such as the anti-lock brakes and the fuel-injection system. Each of these systems is controlled by a microprocessor. Yes, even the black, hardened blob that looks like a dried-up and pressed-down piece of gum inside a musical greeting card is a microprocessor. There are generally two types of microprocessors: general-purpose microprocessors and dedicated microprocessors.General-purpose microprocessors, such as the Pentium CPU, can perform different tasks under the control of software instructions. General-purpose microprocessors are used in all personal computers.

## II. THE INTEL 486 FAMILY

When Intel finally did catch up, it did so in a big way with the release of the 80486 processor, better known as the 486, in 1989. In addition to adding an 8K primary cache, Intel decided to integrate a floating-point math coprocessor (FPU) to an improved 386 core with scalar architecture, and a full 32-bit data and address bus width. Because of the high transistor count, which numbered 1.2 million, the infant mortality rate was high. At first, only 30 percent of the chips survived the testing process from start to finish. Most of the failures occurred in the math coprocessor section, which occupied about two-third of the chip's real estate.

So it took no time at all for Intel to switch to testing its 486 chips for CPU performance first, and follow up with a math coprocessor check. Those chips that passed the first phase but flunked the math were labeled 486SX, and went into lower-priced, conventional desktops without math processors. Those chips that passed their math tests went into a higher-priced model, now called the 486DX. As yields improved, and demand for the lower-priced 486SX increased, the 486SX selection process was winnowed down to testing the CPU only, with a subsequent blowing of the fuse that fed power to the math coprocessor (just in case the math coprocessor was functional, but flawed). Another important feature of the 486 line was the introduction of 3.3volt technology — something that Motorola couldn't match until two years later. Up to 1990 microprocessor logic was based on a 5-volt power supply. However, the amount of heat a semiconductor generates is a function of speed multiplied by voltage. By 1990, the speed of computer chips (both microprocessors and external logic chips) hit a heat barrier — if they went any faster, they'd simply burn up. Reducing the voltage reduced the heat build-up and let the chips run faster. By the year 2000, its expected computer chips will run at 500 MHz using 0.9-volt power sources. What was Motorola doing all this time? It was busy working on the 68060, a third generation 68000 chip that introduced the concept of superscalar pipelining, a technique again borrowed from mainframe technology, which permits multiple instructions to run at the same time. This chip saw the light of day in early 1994. Motorola was also busy developing a line of microcontroller chips, like the 68HC11.

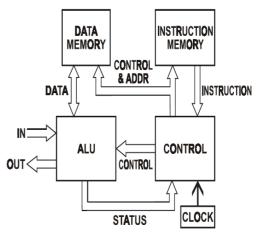

Figure 1.2:-Harvard Architecture Microprocess

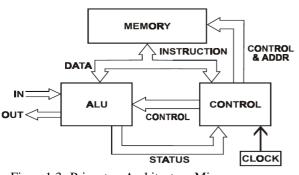

Figure 1.3:-Princeton Architecture Microprocessor

#### III. CODING OF MICROPROCESSOR MULTIPLEXER

```

A. 2*1 4-bit multiplexer :-

libraryieee;

use ieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

useieee.numeric_std.all;

entity mux2 is port (

s: in std_logic;

x0, x1: in std_logic_vector(3 downto 0);

y: out std_logic_vector(3 downto 0);

end mux2;

```

architecture imp of mux2 iss begin process(s, x0, x1) begin if(s= '0') then  $y \le x0$ ; else  $y \le x1$ ; end if; end process; end imp;

B. 4\*1 8-bit multiplexer:libraryieee; use ieee.std\_logic\_1164.all; useieee.std\_logic\_unsigned.all; useieee.numeric\_std.all; entity mux2 is port ( in std\_logic\_vector(1 downto 0); s: x0, x1, x2, x3: in std\_logic\_vector(7 downto 0); y: out std\_logic\_vector(7 downto 0); end mux4; architecture imp of mux4 is begin process(s, x0, x1, x2, x3) begin case s is when "00" =>y <= x0; when "01" => $y \le x_1$ ; when "10" => y <= x2;when "11"  $=>_{y} <= x3;$ when others => y <= (others => x'); end case;

end process; end imp; C. Full Adder:libraryieee; use ieee.std logic 1164.all; useieee.std\_logic\_unsigned.all; entity FA is port ( carryIn: in std\_logic; carryOut: out std\_logic; in std logic; x, y: out std\_logic); s: end FA; architecture imp of FA is begin s <= x xor y xorcarryIn; carryout<= (x and y) or (carryIn and (x xor y)); end imp; D. Add and Subtract:entity addsub8 pc is port ( A: in std\_logic\_vector(7 downto 0);B: in std\_logic\_vector(7 downto 0); F: out std\_logic\_vector(7 downto 0);Sub: in std\_logic); end addsub8\_pc; architecture imp of addsub8 pc is begin process(A, B, sub) begin if (sub= '0') then  $F \leq A+B;$ else  $F \le A - B;$ end if; end process; end imp; E. Opcode Definition:-PACKAGE opcodes IS SUBTYPE t\_cond1 IS std\_logic\_vector (2 DOWNTO 0); CONTANT sta : t\_cond1 := "000": CONSTANT Ida : t\_cond1 := "001"; CONSTANT movi : t cond1 := "010"; : t cond1 := "011"; CONSTANT inp CONSTANT outp : t cond1 := "100"; CONSTANT jnz : t cond1 := "101";

"110":

CONSTANT adda

CONSTANT suba

: t\_cond1 :=

: t\_cond1 :=

| "111";                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | downto 5);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ···· ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ALUSel: out std_logic_vector(1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| SUBTYPE t_org IS std_logic_vecter (4 DOWNTO 0);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | downto 0);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| CONSTANT A : t oreg := " $00000$ ";                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Asel: out std_logic_vector(1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| CONSTANT B : t oreg := "00001";                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | downto 0);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| CONSTANT C : $t \text{ oreg} := "00010";$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | writeAcc: out std_logic;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| CONSTANT D : t oreg := "00011";                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | IRload: out std_logic;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| CONSTANT E : $t \text{ oreg} := ``00100'';$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PCload: out std_logic;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| END opcodes;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Oload: out std_logic;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | jmpMux: out std_logic;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| F. Program Counter:-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | opfetch: out std_logic;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| libraryieee;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | we: out std_logic;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| use ieee.std_logic_1164.all;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | rbe: out std_logic;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| useieee.std_logic_unsigned.all;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | end controller;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| useieee.numeric_std.all;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | architecture imp of controller is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| entity PC is port (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Type state_type is (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| clk: in std_logic;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | s_start,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| reset: in std_logic;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | s_fetch,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| load: in std_logic;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | s_decode,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| INPUT: in std_logic_vector(7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | s_jnz,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| downto 0);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | s_in,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| OUTPUT: out std_logic_vector(7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | s_out,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| downto 0));                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | s_add,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| end PC;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | s_sub,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | s_store,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| architecture imp of PC is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | s_load,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| component FF is Port(                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | s_mov);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| clk: in std_logic;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | signal state: state_type := s_start;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| reset: in std_logic;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | signalclkcount: std_logic_vector(7 downto 0);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| load: in std_logic;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | begin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| D: in std_logic;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | NEXT_STATE_LOGIC: process(reset, clk)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Q: in std_logic);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | begin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| end component;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | if(reset= '1') then                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| begin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | state<= s_start;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| U0: FF port map (clk, reset, load, INPUT(0),                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | clkcount<= X"00";                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| U0: FF port map (clk, reset, load, INPUT(0), OUTPUT(0));                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | clkcount<= X"00";<br>elsif(clk ' event and clk='1') then                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| U0:FF port map (clk, reset, load, INPUT(0),OUTPUT(0));FF port map (clk, reset, load, INPUT(1),                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | clkcount<= X"00";<br>elsif(clk ' event and clk='1') then<br>clkcount<= clkcount + 1;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| U0:FF port map (clk, reset, load, INPUT(0),OUTPUT(0));FF port map (clk, reset, load, INPUT(1),OUTPUT(1));FF port map (clk, reset, load, INPUT(1),                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | clkcount<= X"00";<br>elsif(clk ' event and clk='1') then<br>clkcount<= clkcount + 1;<br>case state is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| U0:FF port map (clk, reset, load, INPUT(0),OUTPUT(0));FF port map (clk, reset, load, INPUT(1),OUTPUT(1));FF port map (clk, reset, load, INPUT(2),U2:FF port map (clk, reset, load, INPUT(2),                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <pre>clkcount&lt;= X"00";<br/>elsif(clk ' event and clk='1') then<br/>clkcount&lt;= clkcount + 1;<br/>case state is<br/>whens_start =&gt; state &lt;= s_fetch:</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| U0:FF port map (clk, reset, load, INPUT(0),OUTPUT(0));FF port map (clk, reset, load, INPUT(1),OUTPUT(1));FF port map (clk, reset, load, INPUT(2),OUTPUT(2));FF port map (clk, reset, load, INPUT(2),                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <pre>clkcount&lt;= X"00";<br/>elsif(clk ' event and clk='1') then<br/>clkcount&lt;= clkcount + 1;<br/>case state is<br/>whens_start =&gt; state &lt;= s_fetch:<br/>whens_fetch =&gt; state &lt;= s_decode;</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| U0:FF port map (clk, reset, load, INPUT(0),OUTPUT(0));FF port map (clk, reset, load, INPUT(1),OUTPUT(1));FF port map (clk, reset, load, INPUT(2),OUTPUT(2));FF port map (clk, reset, load, INPUT(3),U3:FF port map (clk, reset, load, INPUT(3),                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <pre>clkcount&lt;= X"00";<br/>elsif(clk ' event and clk='1') then<br/>clkcount&lt;= clkcount + 1;<br/>case state is<br/>whens_start =&gt; state &lt;= s_fetch:<br/>whens_fetch =&gt; state &lt;= s_decode;<br/>whens_decode =&gt;</pre>                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| U0:FF port map (clk, reset, load, INPUT(0),OUTPUT(0));FF port map (clk, reset, load, INPUT(1),OUTPUT(1));FF port map (clk, reset, load, INPUT(2),OUTPUT(2));FF port map (clk, reset, load, INPUT(3),OUTPUT(3));FF port map (clk, reset, load, INPUT(3),                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <pre>clkcount&lt;= X"00";<br/>elsif(clk ' event and clk='1') then<br/>clkcount&lt;= clkcount + 1;<br/>case state is<br/>whens_start =&gt; state &lt;= s_fetch:<br/>whens_fetch =&gt; state &lt;= s_decode;<br/>whens_decode =&gt;<br/>case IR(7 downto 5) is</pre>                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| U0:FF port map (clk, reset, load, INPUT(0),OUTPUT(0));FF port map (clk, reset, load, INPUT(1),OUTPUT(1));FF port map (clk, reset, load, INPUT(2),OUTPUT(2));FF port map (clk, reset, load, INPUT(3),OUTPUT(3));FF port map (clk, reset, load, INPUT(4),                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <pre>clkcount&lt;= X"00";<br/>elsif(clk ' event and clk='1') then<br/>clkcount&lt;= clkcount + 1;<br/>case state is<br/>whens_start =&gt; state &lt;= s_fetch:<br/>whens_fetch =&gt; state &lt;= s_decode;<br/>whens_decode =&gt;<br/>case IR(7 downto 5) is<br/>when "000" =&gt; state &lt;= s_store;</pre>                                                                                                                                                                                                                                                                                                                                                         |  |

| U0:FF port map (clk, reset, load, INPUT(0),OUTPUT(0));FF port map (clk, reset, load, INPUT(1),OUTPUT(1));FF port map (clk, reset, load, INPUT(2),OUTPUT(2));FF port map (clk, reset, load, INPUT(3),OUTPUT(3));FF port map (clk, reset, load, INPUT(4),OUTPUT(4));FF port map (clk, reset, load, INPUT(4),                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <pre>clkcount&lt;= X"00";<br/>elsif(clk ' event and clk='1') then<br/>clkcount&lt;= clkcount + 1;<br/>case state is<br/>whens_start =&gt; state &lt;= s_fetch:<br/>whens_fetch =&gt; state &lt;= s_decode;<br/>whens_decode =&gt;<br/>case IR(7 downto 5) is<br/>when "000" =&gt; state &lt;= s_store;<br/>when "001" =&gt; state &lt;= s_load;</pre>                                                                                                                                                                                                                                                                                                                |  |

| U0:FF port map (clk, reset, load, INPUT(0),OUTPUT(0));FF port map (clk, reset, load, INPUT(1),U1:FF port map (clk, reset, load, INPUT(1),OUTPUT(1));FF port map (clk, reset, load, INPUT(2),U2:FF port map (clk, reset, load, INPUT(2),OUTPUT(2));FF port map (clk, reset, load, INPUT(3),OUTPUT(3));FF port map (clk, reset, load, INPUT(4),OUTPUT(4));FF port map (clk, reset, load, INPUT(5),                                                                                                                                                                                                                                                                                                                                                                                                                          | <pre>clkcount&lt;= X"00";<br/>elsif(clk ' event and clk='1') then<br/>clkcount&lt;= clkcount + 1;<br/>case state is<br/>whens_start =&gt; state &lt;= s_fetch:<br/>whens_fetch =&gt; state &lt;= s_decode;<br/>whens_decode =&gt;<br/>case IR(7 downto 5) is<br/>when "000" =&gt; state &lt;= s_store;<br/>when "001" =&gt; state &lt;= s_load;<br/>when "010" =&gt; state &lt;= s_mov;</pre>                                                                                                                                                                                                                                                                        |  |

| U0:         FF port map (clk, reset, load, INPUT(0),           OUTPUT(0));         FF port map (clk, reset, load, INPUT(1),           U1:         FF port map (clk, reset, load, INPUT(1),           OUTPUT(1));         FF port map (clk, reset, load, INPUT(2),           OUTPUT(2));         FF port map (clk, reset, load, INPUT(3),           OUTPUT(3));         FF port map (clk, reset, load, INPUT(4),           OUTPUT(4));         FF port map (clk, reset, load, INPUT(4),           OUTPUT(4));         FF port map (clk, reset, load, INPUT(5),           OUTPUT(5));         FF port map (clk, reset, load, INPUT(5),                                                                                                                                                                                      | <pre>clkcount&lt;= X"00";<br/>elsif(clk ' event and clk='1') then<br/>clkcount&lt;= clkcount + 1;<br/>case state is<br/>whens_start =&gt; state &lt;= s_fetch:<br/>whens_fetch =&gt; state &lt;= s_decode;<br/>whens_decode =&gt;<br/>case IR(7 downto 5) is<br/>when "000" =&gt; state &lt;= s_store;<br/>when "001" =&gt; state &lt;= s_load;<br/>when "010" =&gt; state &lt;= s_mov;<br/>when "011" =&gt; state &lt;= s_in;</pre>                                                                                                                                                                                                                                 |  |

| U0:FF port map (clk, reset, load, INPUT(0),OUTPUT(0));FF port map (clk, reset, load, INPUT(1),U1:FF port map (clk, reset, load, INPUT(1),OUTPUT(1));FF port map (clk, reset, load, INPUT(2),U2:FF port map (clk, reset, load, INPUT(2),OUTPUT(2));FF port map (clk, reset, load, INPUT(3),OUTPUT(3));FF port map (clk, reset, load, INPUT(4),OUTPUT(4));FF port map (clk, reset, load, INPUT(5),OUTPUT(5));FF port map (clk, reset, load, INPUT(6),                                                                                                                                                                                                                                                                                                                                                                       | <pre>clkcount&lt;= X"00";<br/>elsif(clk ' event and clk='1') then<br/>clkcount&lt;= clkcount + 1;<br/>case state is<br/>whens_start =&gt; state &lt;= s_fetch:<br/>whens_fetch =&gt; state &lt;= s_decode;<br/>whens_decode =&gt;<br/>case IR(7 downto 5) is<br/>when "000" =&gt; state &lt;= s_store;<br/>when "001" =&gt; state &lt;= s_load;<br/>when "010" =&gt; state &lt;= s_mov;<br/>when "011" =&gt; state &lt;= s_in;<br/>when "100" =&gt; state &lt;= s_out;</pre>                                                                                                                                                                                         |  |